Product Summary

The DP83816AVNG is a single-chip 10/100 Mb/s Ethernet Controller for the PCI bus. It is targeted at low-cost, high volume PC motherboards, adapter cards, and embedded systems. The DP83816AVNG fully implements the V2.2 33 MHz PCI bus interface for host communications with power management support. Packet descriptors and data are transferred via bus-mastering, reducing the burden on the host CPU. The DP83816AVNG can support full duplex 10/100 Mb/s transmission and reception, with minimum interframe gap. The device is an integration of an enhanced version of the National Semiconductor PCI MAC/BIU(Media Access Controller/Bus Interface Unit) and a 3.3V CMOS physical layer interface.

Parametrics

DP83816AVNG absolute maximum ratings: (1)Supply Voltage (VDD): -0.5 V to 3.6 V; (2)DC Input Voltage (VIN): -0.5 V to 5.5 V; (3)DC Output Voltage (VOUT): -0.5 V to VDD + 0.5 V; (4)Storage Temperature Range (TSTG): -65 ℃ to 150 ℃; (5)Power Dissipation (PD): 504 mW; (6)Lead Temp. (TL) (Soldering, 10 sec): 260 ℃; (7)ESD Rating (RZAP = 1.5kΩ, CZAP = 120 pF): 2.0 KV; (8)ESD for TPTD + pins only: 1.0 KV; (9)θja (@0 cfm, 0.5 Watt): 46.4 ℃/W; (10)θjc (@1 Watt): 9.29 ℃/W.

Features

DP83816AVNG features: (1)IEEE 802.3 Compliant, PCI V2.2 MAC/BIU supports traditional data rates of 10 Mb/s Ethernet and 100 Mb/s Fast Ethernet (via internal phy); (2)Bus master - burst sizes of up to 128 dwords (512 bytes); (3)BIU compliant with PC 97 and PC 98 Hardware Design Guides, PC 99 Hardware Design Guide draft, ACPI v1.0, PCI Power Management Specification v1.1, OnNow Device Class Power Management Reference Specification - Network Device Class v1.0a; (4)Wake on LAN (WOL) support compliant with PC98, PC99, SecureOn, and OnNow, including directed packets, Magic Packet, VLAN packets, ARP packets, pattern match packets, and Phy status change; (5)Clkrun function for PCI Mobile Design Guide; (6)Virtual LAN (VLAN) and long frame support; (7)Support for IEEE 802.3x Full duplex flow control; (8)Extremely flexible Rx packet filtration including: single address perfect filter with MSb masking, broadcast, 512 entry multicast/unicast hash table, deep packet pattern matching for up to 4 unique patterns; (9)Statistics gathered for support of RFC 1213 (MIB II), RFC 1398 (Ether-like MIB), IEEE 802.3 LME, reducing CPU overhead for management.

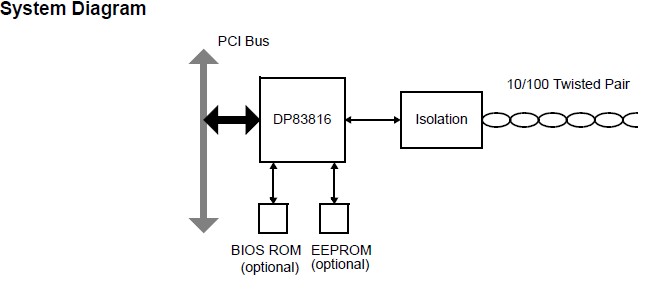

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

DP83816AVNG |

National Semiconductor (TI) |

Ethernet ICs |

Data Sheet |

|

|

||||||||||||

|

DP83816AVNG/63SN |

National Semiconductor (TI) |

Ethernet ICs |

Data Sheet |

|

|

||||||||||||

|

DP83816AVNG/NOPB |

National Semiconductor (TI) |

Clock Generators & Support Products INTEGR PCI ETHERNET MAC & PHYS LAYER |

Data Sheet |

|

|

||||||||||||

|

DP83816AVNG-EX/NOPB |

National Semiconductor (TI) |

Ethernet ICs |

Data Sheet |

|

|

||||||||||||

(Hong Kong)

(Hong Kong)